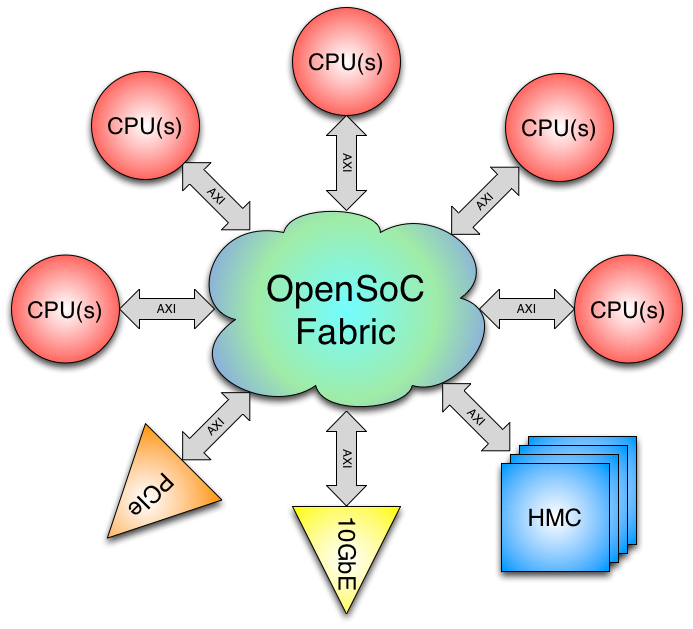

The OpenSoC Fabric is an ongoing project to create a open source network-on-chip generator capable of creating a synthesizeable network for connecting processors, memory and I/O devices.

The OpenSoC Fabric is based on the AXI-Lite bus standard allowing easy connections to ARM and ARM compatible devices.

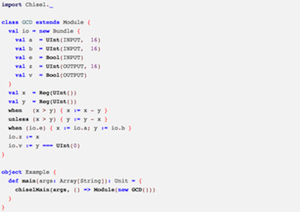

OpenSoC Fabric is written in the Chisel HDL providing both a C++ functional model and a Verilog Hardware Description

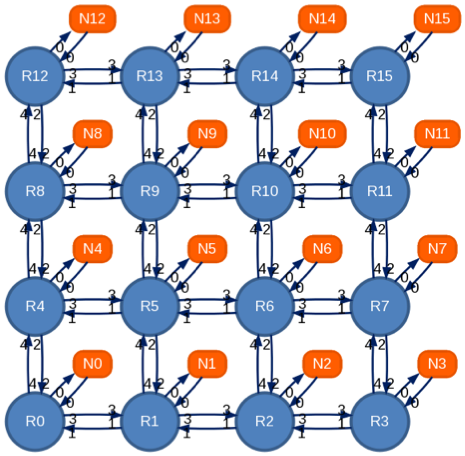

Experiment with multiple topologies using the OpenSoC Fabric. The framework is designed to efficiently implement a range of popular on-chip network topologies.